# Typ3 osa / PNC iPCL System Description and Programming Manual

Rexroth Bosch Group Тур3 osa / PNC

# iPCL System Description and Programming Manual

1070 073 875-101 (02.04) GB

Software release: V7.x

© 2002

by Bosch Rexroth AG, Erbach / Germany All rights reserved, including applications for protective rights. Reproduction or distribution by any means subject to our prior written permission.

Discretionary charge 12.- EUR

# Contents

# Page

V

| <b>1</b><br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6                                                                                         | Safety InstructionsIntended useQualified personnelSafety markings on productsSafety instructions in this manualSafety instructions for the described productDocumentation, software release and trademarks                                                                                                                                                                                  | <b>1–1</b><br>1–1<br>1–2<br>1–3<br>1–4<br>1–5<br>1–7                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| <b>2</b><br>2.1<br>2.2<br>2.3<br>2.4                                                                                                       | System Overview<br>Functionality<br>Hardware platforms<br>iPCL extensions<br>Data backup                                                                                                                                                                                                                                                                                                    | <b>2–1</b><br>2–2<br>2–3<br>2–4                                                                                                           |

| <b>3</b><br>3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6                             | ConfigurationConnecting to the systemStartup of the iPCLInitialization of the iPCLStartup diagramStartup conditionsData backup and residual characteristics of the iPCLData backup depending on hardware platformDefining residual areas in the OM2Residual characteristics depending on hardware platformResidual operationNon-residual operationBuffer failure, data backup fault         | <b>3–1</b><br>3–1<br>3–2<br>3–3<br>3–4<br>3–7<br>3–9<br>3–9<br>3–12<br>3–14<br>3–15<br>3–15<br>3–16                                       |

| <b>4</b><br>4.1<br>4.2                                                                                                                     | <b>Peripheral Operation</b> Data exchange machine <—> PLC PROFIBUS-DP                                                                                                                                                                                                                                                                                                                       | <b>4–1</b><br>4–1<br>4–2                                                                                                                  |

| <b>5</b><br>5.1<br>5.2<br>5.3<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.5<br>5.6<br>5.6.1<br>5.6.2<br>5.6.3<br>5.6.4<br>5.7<br>5.7.1<br>5.8 | Programming Basics<br>Program Structure<br>Module Types<br>Organization modules (OM)<br>Program modules<br>Data modules<br>APS modules<br>Program Processing<br>Time Monitoring<br>I/O state<br>Fixing inputs, outputs & markers<br>Updating timers<br>Cyclical processing<br>Application program structure<br>Initialisation table OM2<br>Printout of the OM2iPCL<br>Module reference list | <b>5–1</b><br>5–1<br>5–2<br>5–2<br>5–3<br>5–3<br>5–3<br>5–4<br>5–6<br>5–6<br>5–6<br>5–6<br>5–6<br>5–7<br>5–7<br>5–7<br>5–8<br>5–9<br>5–14 |

| 5.9    | Module existence                                       | 5–15 |

|--------|--------------------------------------------------------|------|

| 5.10   | Module size                                            | 5–15 |

| 5.11   | Module start address                                   | 5–16 |

| 5.12   | Module header                                          | 5–16 |

| 5.13   | OM9 error module                                       | 5–17 |

| 5.14   | Fixation                                               | 5–17 |

| 5.15   | Parameterized Modules                                  | 5–18 |

| 5.16   | Time-controlled program processing                     | 5–19 |

| 5.17   | Application stack                                      | 5–20 |

| 6      | iPCL addressing                                        | 6–1  |

| 6.1    | Operand & module identifiers, module list              | 6–1  |

| 6.2    | Assignments in the special marker area                 | 6–2  |

| 6.3    | System area assignment                                 | 6–4  |

| 6.4    | Periphery status                                       | 6–6  |

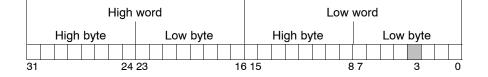

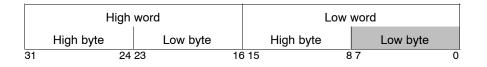

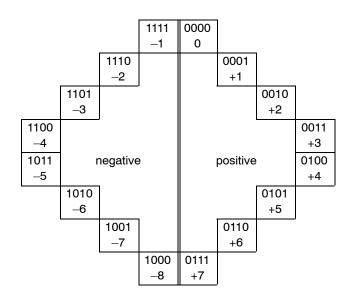

| 6.5    | Data formats                                           | 6–7  |

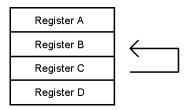

| 6.6    | Register structure                                     | 6–11 |

| 6.7    | Representation of constants                            | 6–12 |

| 6.8    | Program module calls                                   | 6–12 |

| 6.9    | Jump instructions                                      | 6–12 |

| 6.10   | Bit- and module addresses                              | 6–13 |

| 6.11   | Byte addresses                                         | 6–13 |

| 6.12   | Addressing modes                                       | 6–14 |

| 6.12.1 | Absolute addressable operands                          | 6–14 |

| 6.12.2 | Direct addressing of all absolute addressable operands | 6–14 |

| 6.12.3 | Register-to-register addressing                        | 6–14 |

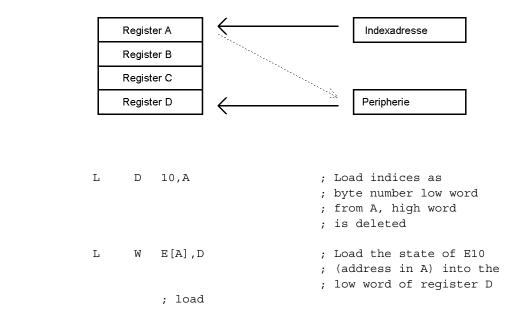

| 6.12.4 | Register indirect addressing                           | 6–15 |

| 6.12.5 | iPCL indirect addressing                               | 6–16 |

| 6.13   | Parameter transfer                                     | 6–18 |

| 6.14   | Addressing limits                                      | 6–19 |

| 7      | Instruction set                                        | 7–1  |

| 7.1    | Structure of controller instructions                   | 7–1  |

| 7.2    | Flags                                                  | 7–1  |

| 7.3    | Key to abbreviations                                   | 7–2  |

| 7.4    | Bit instructions                                       | 7–3  |

|        |                                                        |      |

| 7.2    | Flags                                           | 7–1  |

|--------|-------------------------------------------------|------|

| 7.3    | Key to abbreviations                            | 7–2  |

| 7.4    | Bit instructions                                | 7–3  |

| 7.5    | Timer programming                               | 7–4  |

| 7.5.1  | Timer instructions                              | 7–5  |

| 7.5.2  | Time format                                     | 7–6  |

| 7.5.3  | Timer diagrams                                  | 7–7  |

| 7.6    | Counter instructions                            | 7–8  |

| 7.7    | Digital links                                   | 7–9  |

| 7.8    | SWAP instructions                               | 7–9  |

| 7.9    | Compare instruction                             | 7–10 |

| 7.10   | Load instructions                               | 7–12 |

| 7.11   | Tranfer instructions                            | 7–13 |

| 7.12   | Convert instructions                            | 7–14 |

| 7.13   | Increment & Decrement instructions              | 7–15 |

| 7.14   | Stack instructions                              | 7–15 |

| 7.15   | No operation instructions & CARRY manipulations | 7–15 |

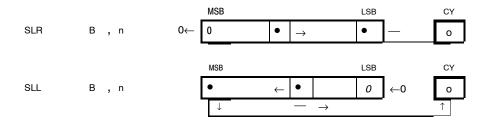

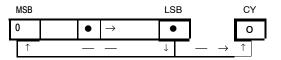

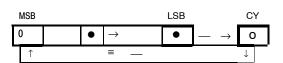

| 7.16   | Shift instructions                              | 7–16 |

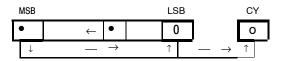

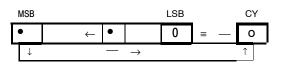

| 7.17   | Rotate instructions                             | 7–17 |

| 7.18   | Fixed point arithmetic                          | 7–18 |

| 7.18.1 | Add instructions                                | 7–18 |

| 7.18.2 | Substract instructions                          | 7–20 |

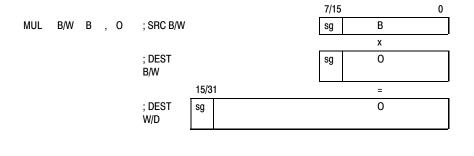

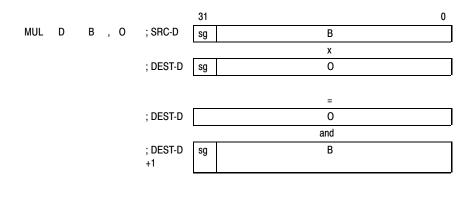

| 7.18.3 | Multiply instructions                           | 7–22 |

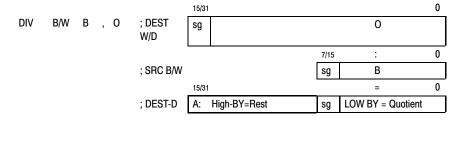

| 7.18.4 | Divide instructions                             | 7–23 |

| 7.19.2       TRANSFERfloating point values       7-24         7.19.3       CONVERT number formats (floating point <-> integer)       7-24         7.19.4       Convert data formats (fleAL <-> LREAL)       7-24         7.19.5       Removing decimal positions       7-22         7.19.6       Comparefloating point values       7-22         7.19.7       Calculating with floating point values       7-22         7.19.8       Forming absolute value       7-22         7.19.9       Extracting square root       7-22         7.19.10       Exponentiation       7-22         7.19.11       Logarithmic functions       7-33         7.20       Parameter assignments       7-33         7.21       Local symbol names & auxiliary markers for program tracking       7-33         7.22       System variable       7-33         7.23       Jump instructions       7-33         7.24       Module calls       7-33         7.25       End of module instruction       7-34         7.26       FIFO instructions       7-34         7.28       Interrupt instructions for time-controlled processing       7-44         7.26       FIFO instructions for time-controlled processing       7-44         7.30                                       | 7.19    | Floating point arithmetic                                     | 7–24 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------------------|------|

| 7.19.3       CONVERT number formats (floating point <-> integer)       7-24         7.19.4       Convert data formats (REAL <> LREAL)       7-21         7.19.5       Removing decimal positions       7-22         7.19.6       Comparefloating point values       7-22         7.19.7       Calculating with floating point values       7-22         7.19.8       Forming absolute value       7-24         7.19.9       Extracting square root       7-22         7.19.1       Logarithmic functions       7-32         7.19.1       Logarithmic functions floating point       7-33         7.19.1       Trigonometric functions floating point       7-34         7.19.1       Logarithmic functions       7-33         7.20       Parameter assignments       7-33         7.21       Local symbol names & auxiliary markers for program tracking       7-33         7.22       System variable       7-34         7.23       Jump instructions       7-34         7.24       Module calls       7-34         7.25       End of module instruction       7-34         7.26       FIFO instructions for time-controlled processing       7-44         7.29       Program stop and program end       7-44         7.                                 |         |                                                               | 7–25 |

| 7.19.4       Convert data formats (REAL <> LREAL)       7-24         7.19.5       Removing decimal positions       7-27         7.19.6       Comparefloating point values       7-22         7.19.7       Calculating with floating point values       7-22         7.19.8       Forming absolute value       7-22         7.19.7       Calculating with floating point values       7-24         7.19.8       Forming absolute value       7-24         7.19.9       Extracting square root       7-24         7.19.10       Exponentiation       7-24         7.19.11       Logarithmic functions       7-34         7.20       Parameter assignments       7-33         7.21       Local symbol names & auxiliary markers for program tracking       7-33         7.22       System variable       7-33         7.23       Jump instructions       7-33         7.24       Module calls       7-33         7.25       End of module instruction       7-33         7.26       FIFO instructions for time-controlled processing       7-44         7.25       End of module instruction s for time-controlled processing       7-44         7.29       Program stop and program end       7-44         7.30                                             |         |                                                               |      |

| 7.19.5       Removing decimal positions       7-22         7.19.6       Comparefloating point values       7-22         7.19.7       Calculating with floating point values       7-22         7.19.8       Forming absolute value       7-22         7.19.9       Extracting square root       7-22         7.19.10       Exponentiation       7-22         7.19.11       Logarithmic functions       7-33         7.20       Parameter assignments       7-33         7.21       Local symbol names & auxiliary markers for program tracking       7-33         7.22       System variable       7-33         7.23       Jump instructions       7-33         7.24       Module calls       7-33         7.25       End of module instruction       7-34         7.26       FiFO instructions       7-34         7.27       Block commands       7-34         7.28       Interrupt instructions for time-controlled processing       7-44         7.29       Program stop and program end       7-44         7.29       Program stop and program end       7-44         7.30       Backing up and loading residual areas       9-4         9.1       Indirect addressing       9-4                                                                      |         |                                                               |      |

| 7.19.6       Comparefloating point values       7-22         7.19.7       Calculating with floating point values       7-24         7.19.8       Forming absolute value       7-24         7.19.9       Extracting square root       7-24         7.19.10       Exponentiation       7-24         7.19.11       Logarithmic functions       7-30         7.19.12       Trigonometric functions floating point       7-33         7.20       Parameter assignments       7-33         7.21       Local symbol names & auxiliary markers for program tracking       7-33         7.22       System variable       7-33         7.23       Jump instructions       7-34         7.24       Module calls       7-33         7.25       End of module instruction       7-34         7.26       FIFO instructions for time-controlled processing       7-44         7.29       Program stop and program end       7-44         7.29       Program stop and program end       7-44         7.30       Backing up and loading residual areas       7-44         8       Processing Times       9-1         9.1       Indirect addressing       9-2         9.2       Compare instruction examples       9-3                                                      |         |                                                               | 7–26 |

| 7.19.7Calculating with floating point values7-247.19.8Forming absolute value7-287.19.9Extracting square root7-287.19.10Exponentiation7-287.19.11Logarithmic functions7-367.19.12Trigonometric functions floating point7-367.19.12Trigonometric functions floating point7-377.20Parameter assignments7-377.21Local symbol names & auxiliary markers for program tracking7-377.22System variable7-337.23Jump instructions7-367.24Module calls7-337.25End of module instruction7-367.26FIFO instructions for time-controlled processing7-377.27Block commands7-377.28Interrupt instructions for time-controlled processing7-477.30Backing up and loading residual areas7-478Processing Times9-19.1Indirect addressing9-19.2Compare instruction examples9-39.3FIFO instruction examples9-39.3FIFO instruction examples9-3                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |                                                               | 7–27 |

| 7.19.8Forming absolute value7-247.19.9Extracting square root7-227.19.10Exponentiation7-227.19.11Logarithmic functions7-307.19.12Trigonometric functions floating point7-337.20Parameter assignments7-337.21Local symbol names & auxiliary markers for program tracking7-337.22System variable7-337.23Jump instructions7-337.24Module calls7-337.25End of module instruction7-337.26FIFO instructions7-337.27Block commands7-337.28Interrupt instructions for time-controlled processing7-447.29Program stop and program end7-447.30Backing up and loading residual areas7-438Processing Times9-19.1Indirect addressing9-19.2Compare instruction examples9-39.3FIFO instruction examples9-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7.19.6  |                                                               | 7–27 |

| 7.19.9       Extracting square root       7-24         7.19.10       Exponentiation       7-26         7.19.11       Logarithmic functions       7-30         7.19.12       Trigonometric functions floating point       7-30         7.20       Parameter assignments       7-37         7.21       Local symbol names & auxiliary markers for program tracking       7-37         7.22       System variable       7-37         7.23       Jump instructions       7-37         7.24       Module calls       7-36         7.25       End of module instruction       7-36         7.26       FIFO instructions for time-controlled processing       7-37         7.29       Program stop and program end       7-44         7.29       Program stop and program end       7-44         7.30       Backing up and loading residual areas       7-42         8       Processing Times       8-1         9       Sample Programs       9-1         9.1       Indirect addressing       9-2         9.2       Compare instruction examples       9-2         9.3       FIFO instruction examples       9-3         9.3       FIFO instruction examples       9-3         9.3 <td>7.19.7</td> <td>Calculating with floating point values</td> <td>7–28</td> | 7.19.7  | Calculating with floating point values                        | 7–28 |

| 7.19.10       Exponentiation       7-24         7.19.11       Logarithmic functions       7-30         7.19.12       Trigonometric functions floating point       7-30         7.20       Parameter assignments       7-31         7.21       Local symbol names & auxiliary markers for program tracking       7-31         7.22       System variable       7-33         7.23       Jump instructions       7-32         7.24       Module calls       7-33         7.25       End of module instruction       7-33         7.26       FIFO instructions       7-33         7.27       Block commands       7-33         7.28       Interrupt instructions for time-controlled processing       7-41         7.29       Program stop and program end       7-42         7.30       Backing up and loading residual areas       7-42         8       Processing Times       8-1         9       Sample Programs       9-1         9.1       Indirect addressing       9-2         9.2       Compare instruction examples       9-3         9.3       FIFO instruction examples       9-3         9.3       FIFO instruction examples       9-3         9.3       FIFO                                                                                    | 7.19.8  | Forming absolute value                                        | 7–29 |

| 7.19.11Logarithmic functions7-307.19.12Trigonometric functions floating point7-307.20Parameter assignments7-317.21Local symbol names & auxiliary markers for program tracking7-337.22System variable7-337.23Jump instructions7-337.24Module calls7-347.25End of module instruction7-367.26FIFO instructions7-377.27Block commands7-367.28Interrupt instructions for time-controlled processing7-477.29Program stop and program end7-477.30Backing up and loading residual areas7-478Processing Times8-19Sample Programs9-19.1Indirect addressing9-39.2Compare instruction examples9-39.3FIFO instruction examples9-39.4AppendixA-1A.1AbbreviationsA-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7.19.9  | Extracting square root                                        | 7–29 |

| 7.19.11Logarithmic functions7-307.19.12Trigonometric functions floating point7-307.20Parameter assignments7-317.21Local symbol names & auxiliary markers for program tracking7-317.22System variable7-337.23Jump instructions7-337.24Module calls7-337.25End of module instruction7-367.26FIFO instructions7-337.27Block commands7-337.28Interrupt instructions for time-controlled processing7-417.29Program stop and program end7-427.30Backing up and loading residual areas7-428Processing Times8-19Sample Programs9-19.1Indirect addressing9-29.3FIFO instruction examples9-39.4AppendixA-1A.1AbbreviationsA-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7.19.10 | Exponentiation                                                | 7–29 |

| 7.19.12Trigonometric functions floating point7-307.20Parameter assignments7-377.21Local symbol names & auxiliary markers for program tracking7-377.22System variable7-377.23Jump instructions7-377.24Module calls7-377.25End of module instruction7-377.26FIFO instructions7-377.27Block commands7-377.28Interrupt instructions for time-controlled processing7-477.29Program stop and program end7-477.30Backing up and loading residual areas7-478Processing Times8-19Sample Programs9-19.1Indirect addressing9-39.2Compare instruction examples9-39.3FIFO instruction examples9-39.4AppendixA-1A.1AbbreviationsA-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7.19.11 |                                                               | 7–30 |

| 7.20Parameter assignments7-37.21Local symbol names & auxiliary markers for program tracking7-37.22System variable7-37.23Jump instructions7-37.24Module calls7-37.25End of module instruction7-37.26FIFO instructions7-37.27Block commands7-37.28Interrupt instructions for time-controlled processing7-47.29Program stop and program end7-447.30Backing up and loading residual areas7-448Processing Times8-19Sample Programs9-19.1Indirect addressing9-29.3FIFO instruction examples9-39.3FIFO instruction examples9-39.4AppendixA-1AAppendixA-1A.1AbbreviationsA-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7.19.12 |                                                               | 7–30 |

| 7.21Local symbol names & auxiliary markers for program tracking .7-37.22System variable .7-37.23Jump instructions .7-37.24Module calls .7-37.25End of module instruction .7-37.26FIFO instructions .7-37.27Block commands .7-37.28Interrupt instructions for time-controlled processing .7-47.29Program stop and program end .7-47.30Backing up and loading residual areas .7-448Processing Times .8-19Sample Programs .9-19.1Indirect addressing .9-19.2Compare instruction examples .9-39.3FIFO instruction examples .9-39.4Appendix .A-1AAppendix .A-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7.20    |                                                               | 7–31 |

| 7.22       System variable       7-3         7.23       Jump instructions       7-3         7.24       Module calls       7-3         7.25       End of module instruction       7-3         7.26       FIFO instructions       7-3         7.27       Block commands       7-3         7.28       Interrupt instructions for time-controlled processing       7-4         7.29       Program stop and program end       7-4         7.30       Backing up and loading residual areas       7-4         8       Processing Times       8-1         9       Sample Programs       9-1         9.1       Indirect addressing       9-1         9.2       Compare instruction examples       9-2         9.3       FIFO instruction examples       9-3         9.3       FIFO instruction examples       9-3                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7.21    | Local symbol names & auxiliary markers for program tracking . | 7–31 |

| 7.23       Jump instructions       7–33         7.24       Module calls       7–34         7.25       End of module instruction       7–36         7.26       FIFO instructions       7–37         7.27       Block commands       7–37         7.28       Interrupt instructions for time-controlled processing       7–47         7.29       Program stop and program end       7–47         7.30       Backing up and loading residual areas       7–47         8       Processing Times       8–1         9       Sample Programs       9–1         9.1       Indirect addressing       9–1         9.2       Compare instruction examples       9–2         9.3       FIFO instruction examples       9–3         9.3       FIFO instruction examples       9–3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7.22    |                                                               | 7–31 |

| 7.24       Module calls       7-34         7.25       End of module instruction       7-34         7.26       FIFO instructions       7-37         7.27       Block commands       7-37         7.28       Interrupt instructions for time-controlled processing       7-47         7.29       Program stop and program end       7-47         7.30       Backing up and loading residual areas       7-47         8       Processing Times       8-1         9       Sample Programs       9-1         9.1       Indirect addressing       9-1         9.2       Compare instruction examples       9-2         9.3       FIFO instruction examples       9-3         A       Appendix       A-1         A.1       Abbreviations       A-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7.23    |                                                               | 7–32 |

| 7.25End of module instruction7-367.26FIFO instructions7-377.27Block commands7-387.28Interrupt instructions for time-controlled processing7-477.29Program stop and program end7-477.30Backing up and loading residual areas7-478Processing Times8-19Sample Programs9-19.1Indirect addressing9-19.2Compare instruction examples9-29.3FIFO instruction examples9-34AppendixA-1A.1AbbreviationsA-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |                                                               | 7–34 |

| 7.26FIFO instructions7-377.27Block commands7-387.28Interrupt instructions for time-controlled processing7-477.29Program stop and program end7-477.30Backing up and loading residual areas7-478Processing Times8-19Sample Programs9-19.1Indirect addressing9-19.2Compare instruction examples9-29.3FIFO instruction examples9-3AAppendixA-1A.1AbbreviationsA-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |                                                               | 7–36 |

| 7.27Block commands7-387.28Interrupt instructions for time-controlled processing7-47.29Program stop and program end7-47.30Backing up and loading residual areas7-48Processing Times8-19Sample Programs9-19.1Indirect addressing9-19.2Compare instruction examples9-29.3FIFO instruction examples9-3AAppendixA-1A.1AbbreviationsA-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |                                                               | 7–37 |

| 7.28Interrupt instructions for time-controlled processing7-47.29Program stop and program end7-47.30Backing up and loading residual areas7-48Processing Times8-19Sample Programs9-19.1Indirect addressing9-19.2Compare instruction examples9-29.3FIFO instruction examples9-3AAppendixA-1A.1AbbreviationsA-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                               | 7–38 |

| 7.29Program stop and program end7-47.30Backing up and loading residual areas7-428Processing Times8-19Sample Programs9-19.1Indirect addressing9-19.2Compare instruction examples9-29.3FIFO instruction examples9-3AAppendixA-1A.1AbbreviationsA-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |                                                               | 7-41 |

| 7.30Backing up and loading residual areas7-428Processing Times8-19Sample Programs9-19.1Indirect addressing9-19.2Compare instruction examples9-29.3FIFO instruction examples9-3AAppendixA-1A.1AbbreviationsA-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |                                                               | 7-41 |

| 8       Processing Times       8–1         9       Sample Programs       9–1         9.1       Indirect addressing       9–2         9.2       Compare instruction examples       9–2         9.3       FIFO instruction examples       9–3         A       Appendix       A–1         A.1       Abbreviations       A–1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |                                                               | 7–42 |

| 9Sample Programs9–19.1Indirect addressing9–29.2Compare instruction examples9–29.3FIFO instruction examples9–3AAppendix9–3A.1AbbreviationsA–1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7.00    |                                                               | 1 72 |

| 9.1Indirect addressing9–9.2Compare instruction examples9–29.3FIFO instruction examples9–2AAppendix9–2A.1AbbreviationsA–1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8       | Processing Times                                              | 8–1  |

| 9.2       Compare instruction examples       9-2         9.3       FIFO instruction examples       9-2         A       Appendix       9-2         A.1       Abbreviations       A-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9       | Sample Programs                                               | 9–1  |

| 9.2       Compare instruction examples       9-2         9.3       FIFO instruction examples       9-2         A       Appendix       9-2         A.1       Abbreviations       A-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9.1     | Indirect addressing                                           | 9–1  |

| 9.3         FIFO instruction examples         9-3           A         Appendix         A-1           A.1         Abbreviations         A-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9.2     | Compare instruction examples                                  | 9–2  |

| AAppendixA-1A.1AbbreviationsA-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9.3     |                                                               | 9–3  |

| A.1 Abbreviations A-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |                                                               |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Α       | Appendix                                                      | A–1  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | A.1     | Abbreviations                                                 | A–1  |

| A.2 Index A-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | A.2     | Index                                                         | A–2  |

Notes:

# 1 Safety Instructions

Before you start working with the iPCL, we recommend that you thoroughly familiarize yourself with the contents of this manual. Keep this manual in a place where it is always accessible to all users.

### 1.1 Intended use

This manual contains information required for the proper use of this product. However, for reasons of structural clarity, the manual cannot provide exhaustive details regarding all available combinations of functional options. Similarly, it is feasible to consider every conceivable integration or operating scenario within the confines of this manual.

The Typ3 osa and PNC controls serve as

- activate feed drives, spindles and auxiliary axes of a machine tool via SERCOS interface for the purpose of guiding a processing tool along a programmed path to process a workpiece (CNC). Furthermore, a PLC is required with appropriate I/O components which – in communication with the actual CNC – controls the machine processing cycles holistically and acts as a technical safety monitor.

- program contours and the processing technology (path feedrate, spindle speed, tool change) of a workpiece.

Any other application is deemed improper use!

The products described hereunder

- have been developed, manufactured, tested and documented in compliance with the safety standards. These products pose no danger to persons or property if they are used in accordance with the handling stipulations and safety notes prescribed for their configuration, mounting, and proper operation.

- comply with the requirements of

- the EMC Directives (89/336/EEC, 93/68/EEC and 93/44/EEC)

- the Low-Voltage Directive (73/23/EEC)

- the harmonized standards EN 50081-2 and EN 50082-2

- are designed for operation in industrial environments, i.e.

- no direct connection to public low-voltage power supply,

- connection to the medium- or high-voltage system via a transformer.

In residential environments, in trade and commerce as well as small enterprises class A equipment may only be used if the following warning is attached:

□ This is a Class A device. In a residential area, this device may cause radio interference. In such case, the user may be required to introduce suitable countermeasures, and to bear the cost of the same.

The faultless, safe functioning of the product requires proper transport, storage, erection and installation as well as careful operation.

### 1.2 Qualified personnel

The requirements as to qualified personnel depend on the qualification profiles described by ZVEI (central association of the electrical industry) and VDMA (association of German machine and plant builders) in: Weiterbildung in der Automatisierungstechnik edited by: ZVEI and VDMA MaschinenbauVerlag Postfach 71 08 64 D-60498 Frankfurt.

This manual is intended for **project engineers and NC specialists**, who are familiar with programmable logic controllers (PLC). A special knowledge of how to configure and commission electrical equipment is also required

Programming, start and operation as well as the modification of program parameters is reserved to properly trained personnel! This personnel must be able to judge potential hazards arising from programming, program changes and in general from the mechanical, electrical, or electronic equipment.

Interventions in the hardware and software of our products, unless described otherwise in this manual, are reserved to our specialized personnel.

Tampering with the hardware or software, ignoring warning signs attached to the components, or non-compliance with the warning notes given in this manual may result in serious bodily injury or material damage.

Only electrotechnicians as recognized under IEV 826-09-01 (modified) who are familiar with the contents of this manual may install and service the products described.

Such personnel are

- those who, being well trained and experienced in their field and familiar with the relevant norms, are able to analyze the jobs being carried out and recognize any hazards which may have arisen.

- those who have acquired the same amount of expert knowledge through years of experience that would normally be acquired through formal technical training.

With regard to the foregoing, please note our comprehensive range of training courses. For current information, the web shop and online booking of seminars please visit our website http://www.bosch.de/at/didactic. Our training center will be pleased to provide you with further information, telephone: (+49) (0 60 62) 78–258.

# 1.3 Safety markings on products

Warning of dangerous electrical voltage!

DANGER! Corrosive battery acid!

Electrostatically sensitive components!

Hazardous light emissions (optical fibre cable emitters)!

Disconnect mains power before opening!

Lug for connecting PE conductor only!

Connection of shield conductor only

# 1.4 Safety instructions in this manual

#### DANGEROUS ELECTRICAL VOLTAGE

This symbol is used to warn of a **dangerous electrical voltage**. The failure to observe the instructions in this manual in whole or in part may result in **personal injury**.

#### DANGER

This symbol is used wherever insufficient or lacking compliance with instructions may result in **personal injury**.

#### CAUTION

This symbol is used wherever insufficient or lacking compliance with instructions may result in **damage to equipment or data files**.

IF This symbol is used to draw the user's attention to special circumstances.

$\star$  This symbol is used if user activities are required.

| 1.5 | Safety instructions for the described product                                                                                                                                                                                                                                                                                                                |  |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|     | DANGER<br>Danger of life through inadequate EMERGENCY-STOP devices!<br>EMERGENCY-STOP devices must be active and within reach in all<br>system modes. Releasing an EMERGENCY-STOP device must not<br>result in an uncontrolled restart of the system!<br>First check the EMERGENCY-STOP circuit, then switch the system<br>on!                               |  |  |

|     | DANGER<br>Risk of personal injury and equipment damage!<br>Always subject new programmes to initial tests while inhibiting axis<br>movements. For this purpose, as a function of the AUTOMATIC<br>mode, the controller provides the option to block axis movements or<br>auxiliary functions by means of special softkey commands.                           |  |  |

|     | DANGER<br>Incorrect or undesired control unit response!<br>Bosch accepts no liability for damage resulting from the execution<br>of an NC program, an individual NC block or the manual movement<br>of axes!<br>Furthermore, Bosch accepts no liability for consequential damage<br>which could have been avoided by programming the PLC appropri-<br>ately! |  |  |

|     | DANGER<br>Retrofits or modifications may adversely affect the safety of the<br>products described!<br>The consequences may include severe injury, damage to equipment,<br>or environmental hazards. Possible retrofits or modifications to the<br>system using third-party equipment therefore have to be approved<br>by Bosch.                              |  |  |

|     | DANGEROUS ELECTRICAL VOLTAGE<br>Unless described otherwise, maintenance works must be performed<br>on inactive systems! The system must be protected against unau-<br>thorized or accidental reclosing.                                                                                                                                                      |  |  |

|     | Measuring or test activities on the live system are reserved to quali-<br>fied electrical personnel!                                                                                                                                                                                                                                                         |  |  |

#### DANGER

Tool or axis movements! Feed and spindle motors generate very powerful mechanical forces and can accelerate very quickly due to their high dynamics.

- Always stay outside the danger area of an active machine tool!

- Never deactivate safety-relevant functions!

- Report any malfunction of the unit to your servicing and repairs department immediately!

#### CAUTION

CAUTION

Use only spare parts approved by Bosch!

# Danger to the module! All ESD protection measures must be observed when using the module! Prevent electrostatic discharges!

The following protective measures must be observed for modules and components sensitive to electrostatic discharge (ESD)!

- Personnel responsible for storage, transport, and handling must have training in ESD protection.

- ESD-sensitive components must be stored and transported in the prescribed protective packaging.

- ESD-sensitive components may only be handled at special ESD-workplaces.

- Personnel, working surfaces, as well as all equipment and tools which may come into contact with ESD-sensitive components must have the same potential (e.g. by grounding).

- Wear an approved grounding bracelet. The grounding bracelet must be connected with the working surface through a cable with an integrated 1 MΩ resistor.

- ESD-sensitive components may by no means come into contact with chargeable objects, including most plastic materials.

- When ESD-sensitive components are installed in or removed from equipment, the equipment must be de-energized.

# 1.6 Documentation, software release and trademarks

#### Documentation

This manual provides details of the programming and operation of the iPCL. Not included are general procedures for project management and installation of controllers and their associated hardware.

| Overview of available documentation                                             | Part no.     |              |  |

|---------------------------------------------------------------------------------|--------------|--------------|--|

|                                                                                 | German       | English      |  |

| Typ3 osa – Interface conditions<br>for project engineering and maintenance      | 1070 073 704 | 1070 073 736 |  |

| Typ3 osa – Software installation                                                | 1070 073 796 | 1070 073 797 |  |

| Decription of functions                                                         | 1070 073 870 | _            |  |

| MACODA<br>Operation and configuration of the machine<br>parameters              | 1070 073 705 | 1070 073 742 |  |

| Operating instructions<br>Standard operator interface                           | 1070 073 726 | 1070 073 739 |  |

| Operating instructions – Diagnostics Tools                                      | 1070 073 779 | 1070 073 780 |  |

| Error Messages                                                                  | 1070 073 798 | 1070 073 799 |  |

| PLC project planning manual,<br>Software interfaces of the integrated PLC       | 1070 073 728 | 1070 073 741 |  |

| iPCL system description and<br>programming manual                               | 1070 073 874 | 1070 073 875 |  |

| ICL700 system description,<br>Program structure of the integrated PLC<br>ICL700 | 1070 073 706 | 1070 073 737 |  |

| DIN programming manual<br>for programming to DIN 66025                          | 1070 073 725 | 1070 073 738 |  |

| CPL programming manual                                                          | 1070 073 727 | 1070 073 740 |  |

| CPL-Debugger Operating instructions                                             | 1070 073 872 | _            |  |

| Tool Management – Parameterization                                              | 1070 073 782 | 1070 073 793 |  |

| Software PLC<br>Development environment for Windows NT                          | 1070 073 783 | 1070 073 792 |  |

| Measuring cycles for<br>touch-trigger switching probes                          | 1070 073 788 | 1070 073 789 |  |

| Universal Milling Cycles                                                        | _            | 1070 073 795 |  |

In this manual the floppy disk drive always uses drive letter A:, and the hard disk drive always uses drive letter C:.

Special keys or key combinations are shown enclosed in pointed brackets:

- Named keys: e.g., <Enter>, <PgUp>, <Del>

- Key combinations (pressed simultaneously): e.g., <Ctrl> + <PgUp>

#### Release

#### IF The descriptive information contained in this manual applies to: Software version: V7.x

The current release number of the individual software modules can be viewed by selecting the 'Control-Diagnostics' softkey in the 'Diagnostics' group operating mode.

The software version of Windows95 or WindowsNT may be displayed as follows:

1. Click the right mouse button on the My Computer icon on your desktop.

2. Select Properties.

#### Trademarks

All trademarks of software installed on Bosch products upon delivery are the property of the respective manufacturer.

Upon delivery, all installed software is copyright-protected. The software may only be reproduced with the approval of Bosch or in accordance with the license agreement of the respective manufacturer.

$\text{MS-DOS}^{\textcircled{\text{\tiny (8)}}}$  and  $\text{Windows}^{\,\scriptsize{\text{\tiny (M)}}}$  are registered trademarks of Microsoft Corporation.

PROFIBUS® is a registered trademark of the PROFIBUS Nutzerorganisation e.V. (user organization).

SERCOS interface<sup>™</sup> is a registered trademark of the SERCOS interface Joint VDW/ZVEI Working Committee.

# 2 System Overview

### 2.1 Functionality

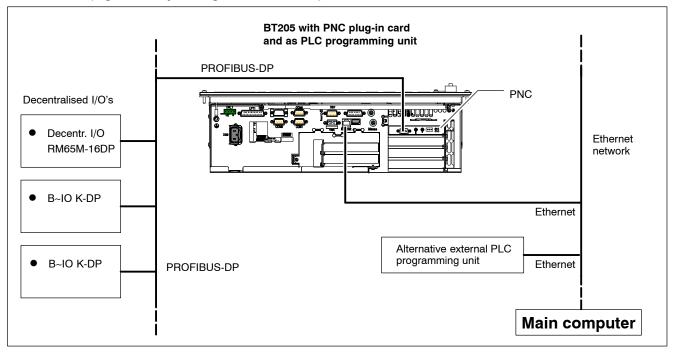

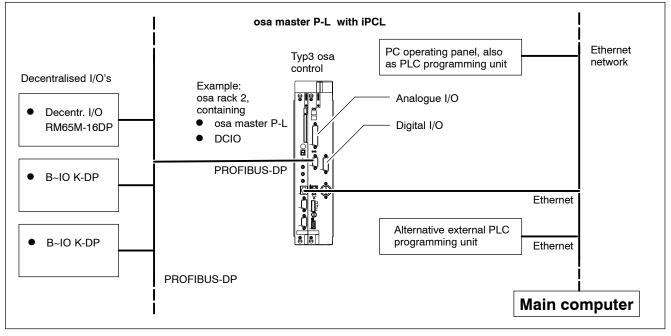

iPCL is a software PLC integrated into the NC control. Without additional hardware iPCL is integrated into:

- the PNC plug-in card

- the type 3 osa component group osa master P-L and osa master P-XL.

Thus a secure functionality is assured independently of Windows.

I/O's are connected via PROFIBUS-DP, enabling RM65M-16DP,  $\,$  B~IO-modules to be used, for example.

For the operation and programming of iPCL, the following configuration software is required:

- WinSPS: Creation of the PLC application program with functional extensions for communication between PLC and NC (APS modules)

- WinDP: Configuration of the PROFIBUS-DP

Communications with the WinSPS, WinDP and other programs are handled by the TCP/IP standard protocol with the use of the BUEP (Bosch transfer protocol) command language.

For the creation of the PLC program or individual program modules in the programming language C, the C compiler and linker are also required.

**□** For additional essentials related to iPCL and to operating decentralized peripherals via the PROFIBUS-DP, refer to the Online Help in WinSPS and WinDP.

## 2.2 Hardware platforms

iPCL is integrated in:

- the PNC plug-in card

- the Typ3 osa component group osa master P-L and osa master P-XL.

#### iPCL in PNC (e.g. in the operating terminal BT205)

#### iPCL in the osa master P-L/XL (Typ3 osa)

#### 2.3 **iPCL** extensions

-

| The maximum I/O area and the PLC user memory (MACODA |

|------------------------------------------------------|

| parameter 2060 00210) are determined by licence:     |

| Туре                              | Peripherals                                     | User memory                                                             |

|-----------------------------------|-------------------------------------------------|-------------------------------------------------------------------------|

| iPCL_1 (PNC)                      | 16 kb for inputs<br>16 kb for outputs           | 32 kbytes                                                               |

| iPCL_2 (PNC)                      | 256 kb for inputs<br>256 kb for outputs         | 128 kbytes                                                              |

| iPCL_3 (PNC)                      | 8 kb for inputs<br>8 kb for outputs             | 512 kbytes                                                              |

| iPCL_4<br>(osa master P-<br>L/XL) | -256 bytes for inputs<br>-256 bytes for outputs | Default: 200 kb depending<br>on free memory in the osa<br>master P-L/XL |

Because the data field and data buffer are included in every hardware expansion level, they do not reduce the size of the user memory! Just like the program and organization modules, the data modules are stored in the PLC user memory.

#### Additional options

OPC server functions are available. It enables MADAP STUDIO to be used together with the PNC.

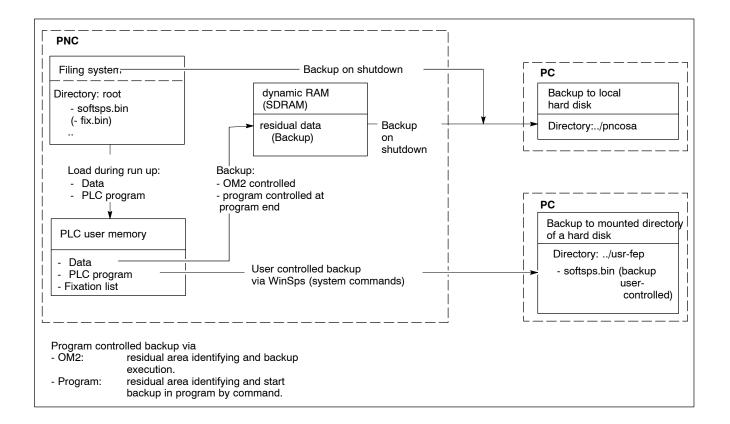

# 2.4 Data backup

PNC

iPCL uses PNC's own memory (SDRAM) and the hard disk of the base unit into which the PNC is plugged.

Optimum functional security of the iPCL in the PNC is attained by using a UPS (uninterruptible power supply), which bridges a potential power loss to allow essential PLC and NC data to be backed up to hard disk and leads to a delayed shut down of the Windows NT operating system.

| SDRAM                                                                                                    |                                         |                                                                                                                                                                                                                 |                                                                                                                                                            |                                                  |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| iPCL memory<br>• PLC program<br>(SoftSPS.bin)<br>• Fixationlist<br>(Fix.bin)<br>• Status<br>(Status.bin) | Data comparis<br>for every<br>amendment | Son<br>Memory for<br>RAM filing system<br>• PLC program<br>(SoftSPS.bin)<br>• Fixation list<br>(Fix.bin)<br>• Status<br>(Status.bin)<br>• Parts program<br>• Machine data<br>Backup<br>on shutdown<br>(as file) | Memory for program<br>execution<br>• residual data<br>and areas and<br>FIFO's<br>Memory for cyclic<br>backup<br>• residual data<br>and areas and<br>FIFO's | Backup by iPCL<br>on shutdown                    |

| Base device (e.g. P(<br>Hard disk<br>Mount directory                                                     | operating pane                          | RAM filing s<br>file:<br>• PLC pro                                                                                                                                                                              | ystem backed up in a<br>ogram (SoftSPS.bin)<br>I list (Fix.bin)                                                                                            | Backup on<br>shutdown<br>after iPCL has<br>ended |

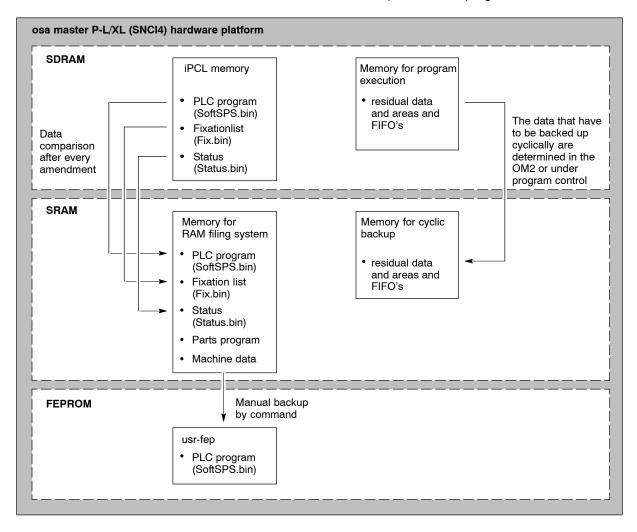

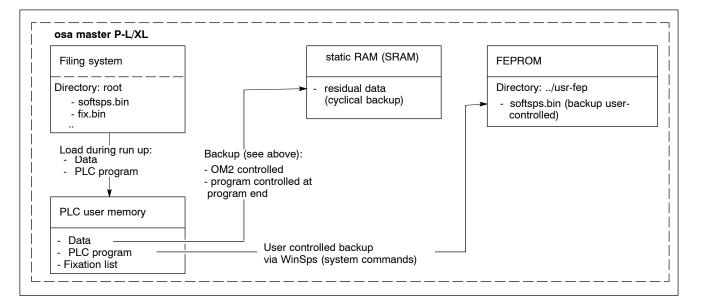

#### osa master P-L/XL (SNCI4)

iPCL uses various memory areas of the component group osa master P-L/XL:

- SDRAM (dynamic mamory) for PLC program and data in use.

- SRAM (static memory) for PLC program and data for switched off control and cyclic backups.

- FEPROM for additional back up of the PLC program.

Notes:

# 3 Configuration

# 3.1 Connecting to the system

### Registering iPCL via MACODA

iPCL has to be registered in the MACODA parameter 2060 00200. Apart from that further parameters can be changed:

- 2060 00200: Selection of the PCL.

- Must be set to iPCL (= 4).

2060 00210: Maximum size of the user program. For the PNC the size may be limited by licence, (for detailed information, refer to Section 2.3)

2060 00211: Max PLC computing time in %. (see Section 8).

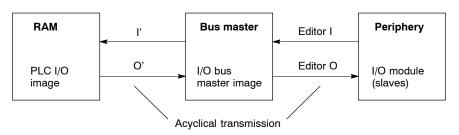

#### Interfacing with Peripherals

The interfacing with peripherals is viy the serial filed bus system **PROFI-BUS-DP** via the PROFIBUS-DP Busmaster interface:

- for base devices with PNC: on the "PNC-PCI card"

- for the Typ3 osa hardware: on the component group "osa dc I/O"

The maximum I/O area is determined by licence.

Reference list:

The bus master monitors the existence of slaves and transfers this data to the iPCL.

Error functions:

The error functions are dependent on the bus system used. The PROFI-BUS-DP field bus features a comprehensive diagnostic system whose messages are made available by the iPCL bus master.

#### System clock management

The system timing, which can be processed in the PLC program via the system area, is generated by the clock source onboard the PC.

# BOSCH

# 3.2 Startup of the iPCL

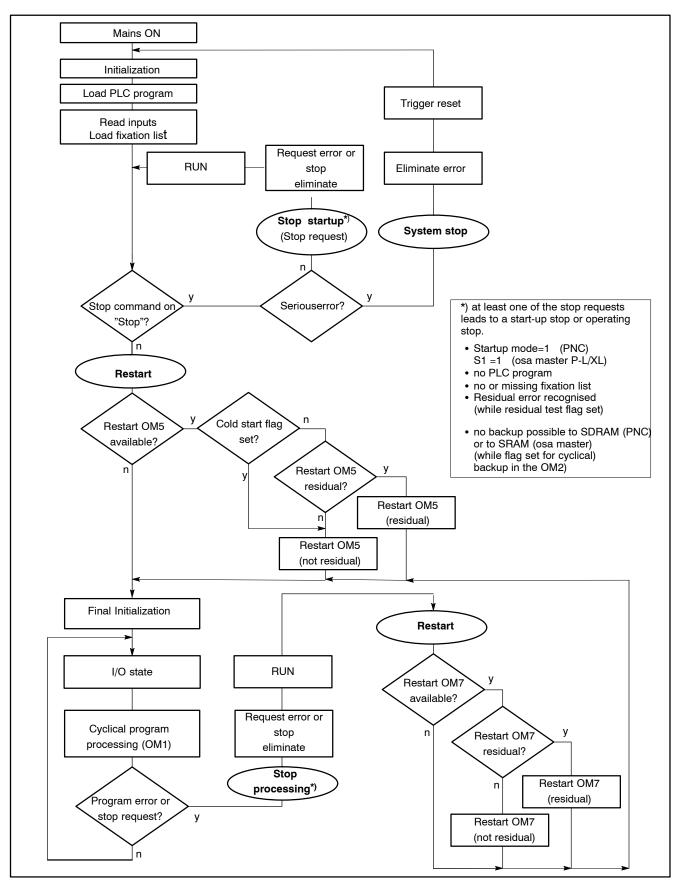

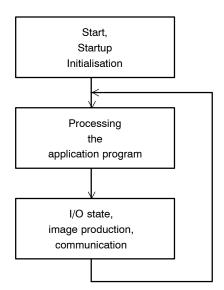

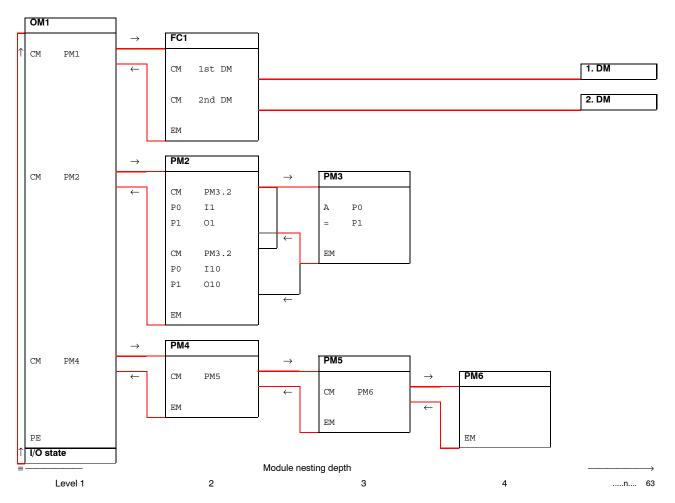

There follows the initialization and the start-up diagram for the iPCL. This procedure is the same for all hardware platforms.

# 3.2.1 Initialization of the iPCL

|                              | In the initiali                                                                                                                                                                               | zation phase the iPCL operating system starts up.                                                                                                                    |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Initializing special markers | The special markers SM21.0 to SM31.7 (see below: "Exceptions") are pre-<br>initialized during "New start" and "Restart". They are subsequently modified<br>in accordance with their function. |                                                                                                                                                                      |

| Initialization values        |                                                                                                                                                                                               |                                                                                                                                                                      |

|                              | SM 26                                                                                                                                                                                         | = FFFF <sub>H</sub>                                                                                                                                                  |

|                              | SM 31.1                                                                                                                                                                                       | = 1                                                                                                                                                                  |

|                              | All others                                                                                                                                                                                    | = 0                                                                                                                                                                  |